# 中国科学技术大学

#### 计算机组成原理

# 课程概要

李曦

Ilxx@ustc.edu.cn

#### 李曦: Who's Who©

- 教师@软件学院/计算机学院

- 博士, 教授, 博导

- 研究方向: 计算机系统结构

- 实时系统,可重构系统,嵌入式智能系统

- 科学问题: 系统的时间行为可预测性与可组合性

#### 大纲

- 课程简介

- 教材选择

- 教学计划

- 成绩考核

- 学习方法

- Learn to do

- Learn to be

- Learn to be with others

- Learn to learn

#### 计算机组成结构,最小的?

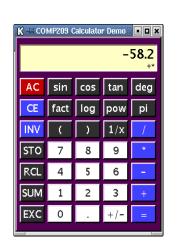

算盘 = 计算器 ≠ 计算机? Tiny?

# 计算机在干啥?

#### 程序如何执行,用到哪些部件?

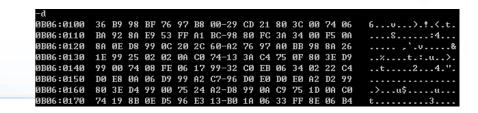

```

数据的表示

/*---sum.c---*/

数据的运算

int sum(int a[], unsigned len)

各类语句的转换与表示(指令)

int i, sum = 0;

各类复杂数据类型的转换表示

for (i = 0; i \le len-1; i++)

过程(函数)调用的转换表示

sum += a[i];

Microsoft Visual C++

return sum;

Unhandled exception in Test.exe: 0xC0000005: Access Violation.

/*---main.c---*/

int main()

确定

int a[1]={100};

int s;

链接(linker)和加载

s=sum(a,0);

程序执行(存储器访问)

printf("%d",s);

异常和中断处理

输入输出(I/O)

```

• C语言计算机?

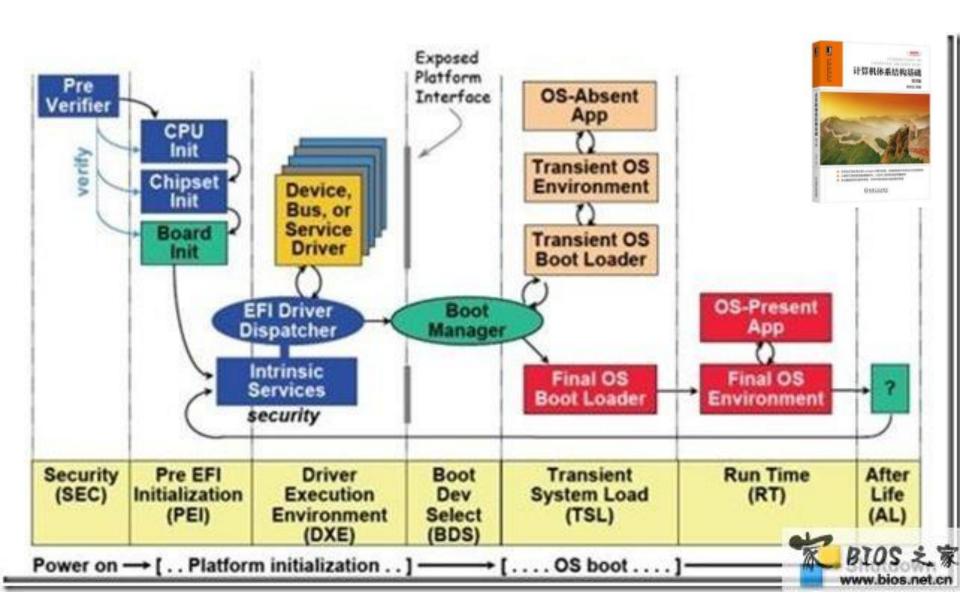

#### 何时开始执行你的C程序? 胡伟武Ch7

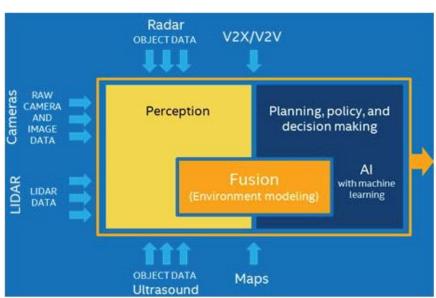

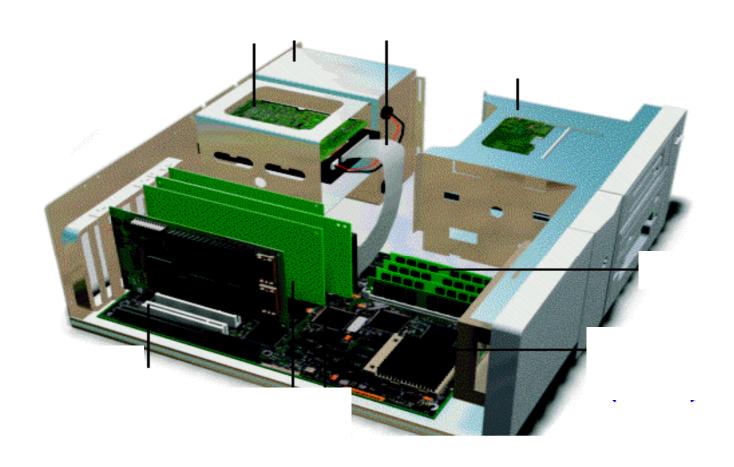

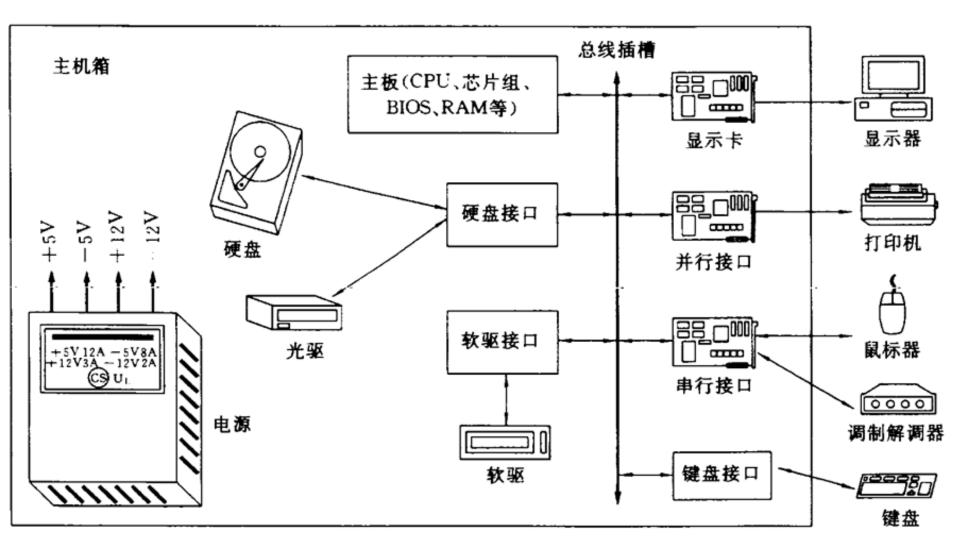

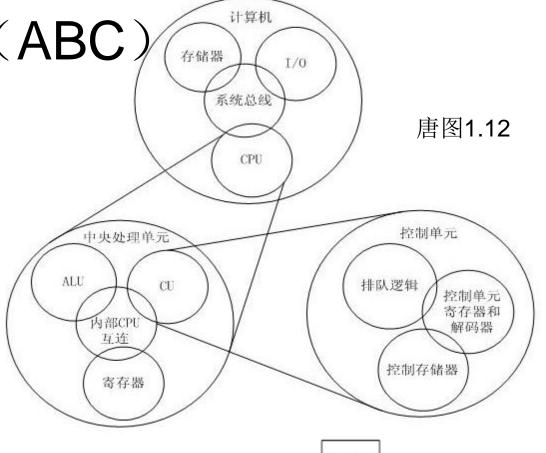

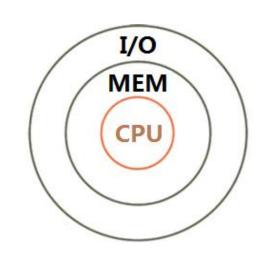

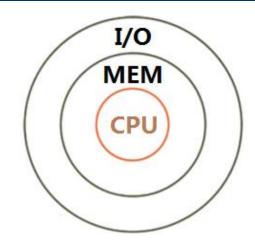

### 计算机组成 (CBD)

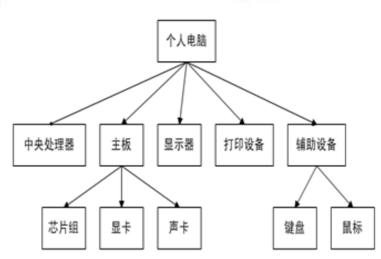

### 计算机组成: 硬件与接口

### 计算机组成:软件与软硬件接口

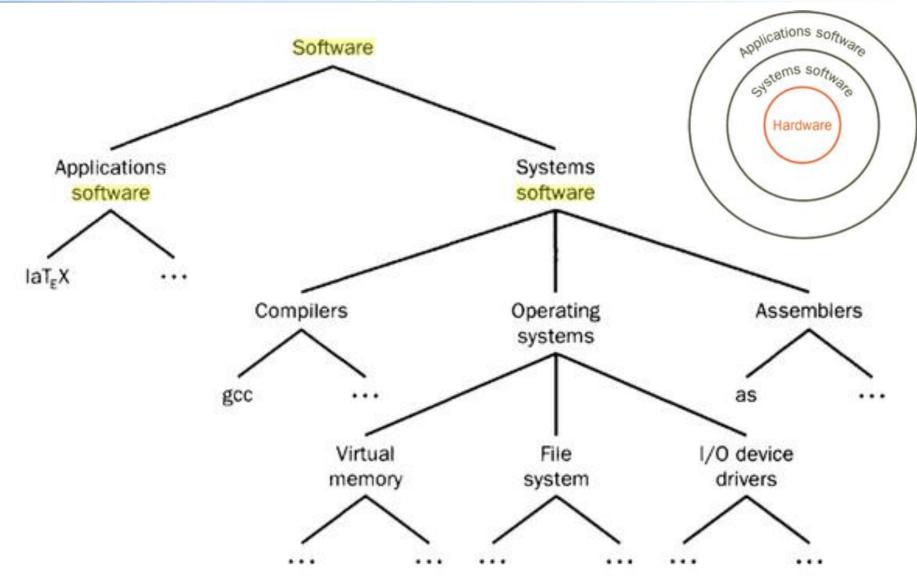

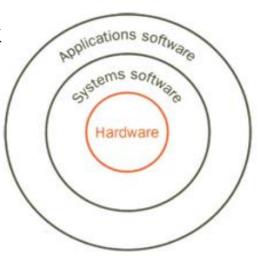

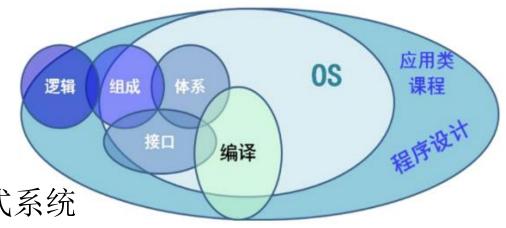

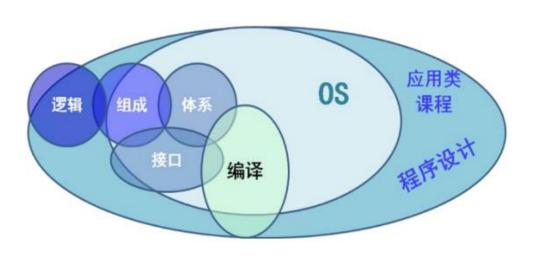

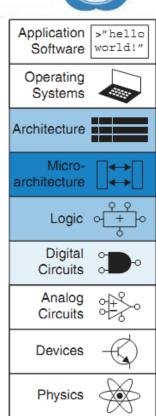

## COD课程的作用: what, how, which

- 专业核心课: 所有专业课的基础

- 所有大学计算机系都开设COD相关课程

- 密切相关课程

- 数字逻辑电路,程序设计

- 组成原理

- 重点"单处理器单核"系统

- 介绍多核、多处理器等并行系统

- 强调软硬件接口

- 体系结构: 量化设计

- 操作系统

- 编译原理

- 微机原理与接口/嵌入式系统

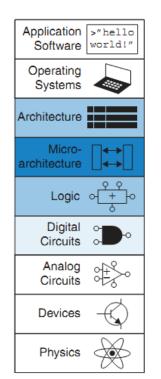

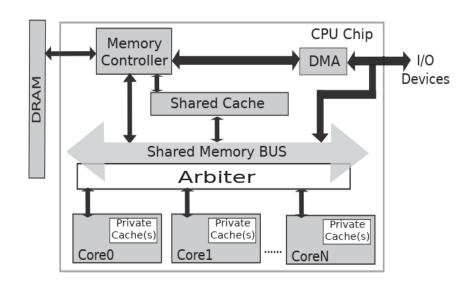

图1-3

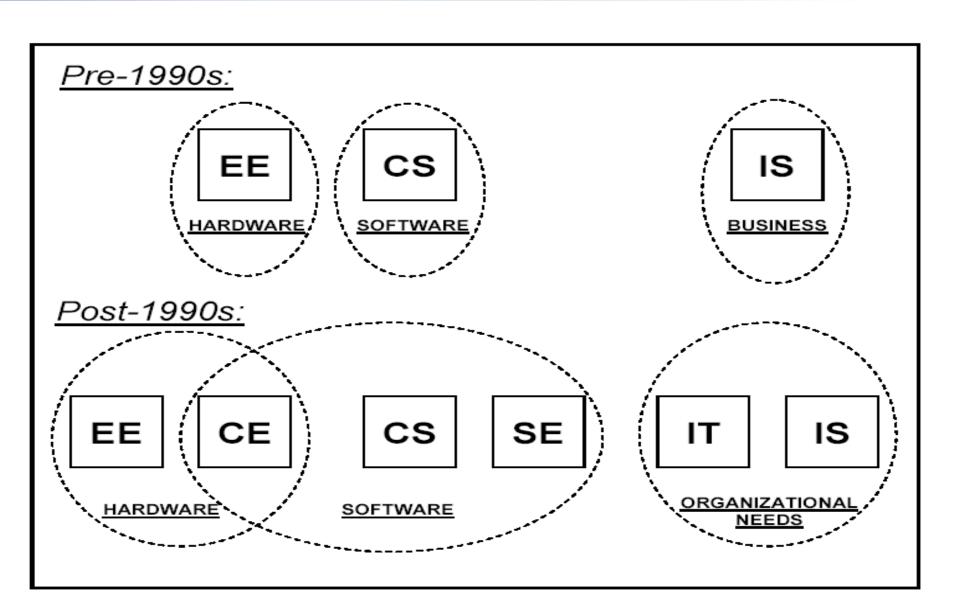

### 课程标准: CS2013/CE2016

- IEEE/ACM Computer Science Curriculum 2013

- ARKA含8个KU(5个必修,3个选修)

- 数字逻辑与系统

- 数据表示

- 汇编级机器组成

- 存储系统组成与结构

- 接口与通信

- 功能组成

- 多处理及结构

- 性能优化

- CE2016增加

- "标准与工具"

- "分布式系统结构,并行与分布式算法"

- 两个层次

- system architecture

- the organization of the computer at the cache and bus level

- organization/microarchitecture

- the internal implementation of a computer at the register and functional unit level

### 课堂教学内容(ABC)

• 中央处理器(CPU)

- 数据表示

- 算术逻辑运算

- 指令系统

- 数据通路

- 控制单元

- 外围部件

- 系统总线

- 总线性能、总线结构、总线控制

- 存储器

- 主存、高速缓存、辅存、虚存

- 输入输出系统

- I/O接口、I/O控制方式、外设

#### 教材与参考书

- 《Computer Organization and Design: The HW-SW I/F》

- David Patterson and John Hennessy, 5th, RV版, 2018/2020

- CPU和Cache强,MEM、总线、I/O弱

- COD涉及并行和性能分析:一些学校用作Computer architecture教材

- 《计算机组成原理》,2nd/3rd,2008/2020,唐朔飞

- 以William Stallings Ed. 4th为框架,参考7th和COD 3rd

- CISC, A模型CPU, 但无OS、VM、并行等内容

- CPU和Cache弱,MEM、总线、I/O强

- "Computer organization and architecture: Designing for performance", COA

- Dr. William Stallings(澳大利亚新南威尔士大学)

- 1996第4版,2000第5版,2003第6版(张昆藏译),2010第8版(彭蔓蔓译)

- 2015第10版(目录同9版,增加一些新资料。电子版)

- The computer system, Arithmetic and logic, The central processing unit

- Parallel organization, including multicore

- The control unit (online!)

- Ed. 8<sup>th</sup>前偏organization,之后偏architecture

- "Guide to Computer Processor Architecture: A RISC-V Approach, with High-Level Synthesis", 2023

#### Patterson and Hennessy 2018图录

| 灵奖

- "COD: The Hardware/ Software Interface"

- 1st Edition, 1994

- 2<sup>nd</sup> Edition, 1997

- 3<sup>rd</sup> Edition, 2004, 郑纬民译

- · Covers the revolutionary change from sequential to parallel computing

- 4<sup>th</sup> Edition, 2009, 2011 康继昌译

- the switch from uniprocessor to multicore microprocessors

- make parallelism a first class citizen(spread parallelism throughout all the chapters)

- 5<sup>th</sup> Edition, 2013 (2016MIPS/ARM, 2018RV64, 2021RV32)

- moves forward into the post-PC era with new examples, exercises, and material highlighting the emergence of mobile computing and the cloud.

- This generational change is emphasized and explored with updated content featuring tablet computers, cloud infrastructure, and the ARM (mobile computing devices) and x86 (cloud computing) architectures.

- features the RISC-V open source instruction set architecture, the first open source architecture designed for use in modern computing environments such as cloud computing, mobile devices, and other embedded systems.

#### 教材主要内容比较

#### COD5: RISC-V

- 1. 计算机概念与工艺

- 2. 指令

- 3. 算逻运算

- 4. RISC处理器

- 单周期、多周期、流水线

- 异常: CP0

- 微程序: COD5 (C.9)

- 5. 存储器层次结构

- SRAM、DRAM、FLASH、DISK

- Cache、Cache控制器

- 可靠性问题(海明码)

- \_ 虚存

- 6. 并行处理器

- 硬件多线程

- 多核

- COD5: "I/O不单独成章"!

- 总线?

- 唐朔飞:以CISC为主

- 第一部分 概论

- 冯诺依曼机,性能指标

- 第二部分 计算机硬件系统

- 总线,内存,Cache,外存,I/O

- 第三部分 CPU

- 算逻运算、ISA, CPU结构, 中断系统

- 介绍了RISC、流水线概念

- 第四部分 CU

- A模型处理器,微操作

- 多周期: 硬连线实现, 微程序实现

- 强调系统完整性:总线/内存/IO

- 唐本无:虚存,并行

- 考研: 唐朔飞or白中英

COD5(CPU、Cache、存储器、异常、MMU)+唐(总线、I/O、中断、DMA)

#### Course Schedule

| Lec. | Topic &                | Read BEFORE c        | lass₊     | <u>Keypoint</u> . |

|------|------------------------|----------------------|-----------|-------------------|

|      |                        | RV64₽                | 唐。        |                   |

| 1 ₽  | 概论→                    | CHP1₽                | 第一、二章↩    | ¢                 |

|      | 逻辑设计基础。                | 4.2、附录A₽             | ¢.        | 自学₽               |

| 2 ₽  | 指令系统。                  | CHP2, 5.14₽          | CHP7 ₽    | 4                 |

|      | 汇编程序设计↩                | 2.12、2.13,COD4 附录 B。 | <b>\$</b> | 冒泡排序。             |

|      | RISC 处理器概述。            | <i>附录</i> D₽         | ¢.        | 4                 |

| 3 ↔  | RISC 数据通路(单周期、多周期)。    | 4.4、RV32 4.5₽        | \$        | 4                 |

| ₽    | 控制器(硬连线,微程序)。          | 附录 C₽                | 微程序 10.2↓ | ę.                |

|      | RISC 数据通路(流水线)。        | 4.5、4.13。            | ÷         | ē.                |

|      | 流水线冒险。                 | 4.6~4.8、4.13 ₽       | \$        | 4                 |

|      | 多发射(超标量),HMT。          | 4.10、6.4             | ¢.        | 4                 |

|      | 异常与中断。                 | 4.9 ₽                | 8.4 🕫     | 4                 |

| 4 ↔  | SRAM, DRAM, ROM, SDRAM | 5.2、A.9₽             | 第四章↩      | ÷                 |

| 42   | Cache ₽                | 5.3、5.4₽             | 4.3 ₽     | ₽                 |

|      | Cache Controllers ₽    | 5.9₽                 | ¢         | ₽                 |

|      | 外存。                    | 5.2, 5.11            | 第四章₽      | 4                 |

|      | 虚存↓                    | 5.7 ₽                | ¢         | ₽                 |

|      | 存储器的可靠性。               | 5.5、5.11、A.9。        | 第四章₽      | 4                 |

| 5 ₽  | 总线↓                    | 6.9 ₽                | 第三章↩      | <b>.</b>          |

| 6 ₽  | I/O &                  | 1.4、6.94             | 第五章↩      | TinyComputer.     |

| 7 ₽  | A 模型 CPU 设计(多周期, 微程序)。 | t)                   | 第八/九/十₽   | ₽                 |

| 8 ₽  | 算术运算。                  | CHP3 ₽               | 第六章₽      | ₽                 |

| 9 ₽  | 专题:并行,非冯机,低功耗。         | CHP1、CHP6₽           | ₽         | ₽                 |

# 课程成绩考核:发现抄袭取消成绩

- 课堂教学: 70%

- 期末考试: 50% (闭卷)

- 作业: 30%, 不能补交!

- 课堂练习: 10%(出勤5%,正确5%)

- 课内实验: 5%

- 冒泡汇编, Tiny系统设计

- 实验报告:参照小论文格式

- 调研: 2~3篇,5%

- 调研报告:参照小论文格式

- 资料来源:参考书、Internet

- 实验课: 30%

#### 课内实验

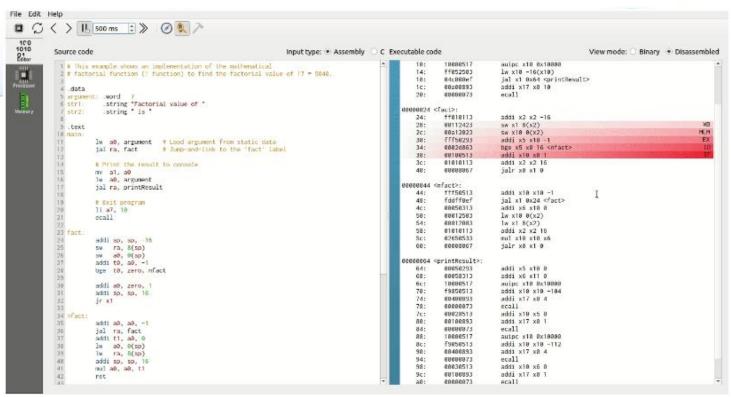

- 【必选】汇编语言程序设计:任意10个数冒泡排序

- 基于RISC-V仿真器Ripes

- 成果要求:

- 报告设计过程、结果(汇编代码、内存数据段映像)、出现的典型问题及解决过程;

- 要求结果体现个人ID: 10个数中含姓名拼音字母

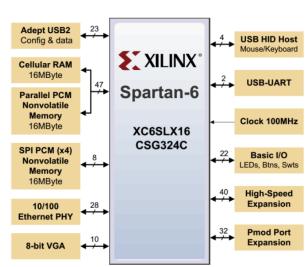

- 【任选】基于Xilinx ISE,设计一个TinyComputer

- 系统硬件组成:包含CPU、on\_chip\_ram和JTAG UART 三个模块;

- 编写并运行一个简单C程序 "hello\_world\_small";

- 成果要求:

- 报告设计过程、结果(原理图、仿真结果、源代码)、出现的典型问题及解决过程;

- 要求结果体现个人ID: "hello\_world\_small—llxx"

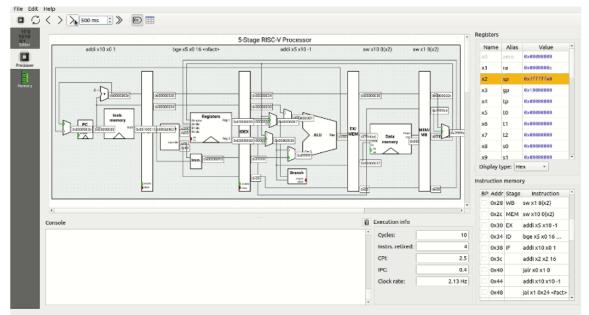

#### Ripes

RV32/64仿真器和汇编器 支持五级ppl 支持Cache? 支持MMIO

Spike (linux) RARS GEM5 SMPCACHE

#### 调研/课内实验: 小论文格式

- 题目(宋体,小二,加粗)

- 姓名、学号(宋体,小四)

- 摘要(宋体,小四)

- 引言(宋体,小四)

- 正文(宋体,小四)

- -问题,过程,结果

- 结论(宋体,小四)

- · 参考文献(宋体,小五) (不少于3篇,中英文皆可)

#### 实验课: 1学分

- Xilinx ISE: 逻辑仿真

- Digilent Nexys3平台

- Spartan-6 FPGA

- 48Mb片外存储器: 含2个非易失相变存储器

- 100 ~200MHz 振荡器 (差分)

- RV32 ISA子集?

- -约40条指令,VerilogHDL

- 单周期/多周期实现(必做)

- 流水线实现(选作)

#### 实验内容与计划(第5-15周)

- 运算与排序(1周)

- 寄存器堆与队列(1周)

- 单周期CPU (1周)

- 多周期CPU (2周)

- 中断与异常(1周)

- 总线与I/O接口(1周)

- 综合设计 (3周)

#### 大纲

- 课程简介

- 教材选择

- 教学计划

- 成绩考核

- 学习方法

- Learn to do

- Learn to be

- Learn to be with others

- Learn to learn

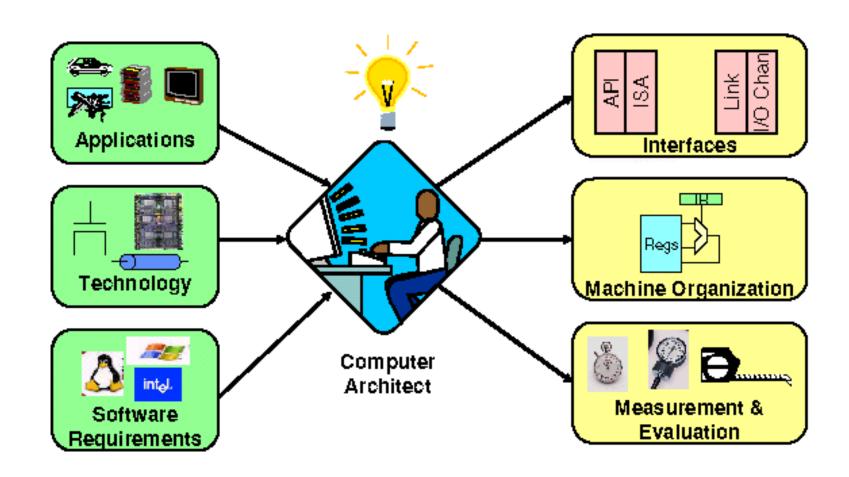

# 课程知识范畴:科学、技术、工程?

#### 计算机系统设计: 3-1-3模型

计算机系统:简单巨系统

计算机科学永恒的问题: 如何设计出更好的计算机, 如何利用好现有的计算机

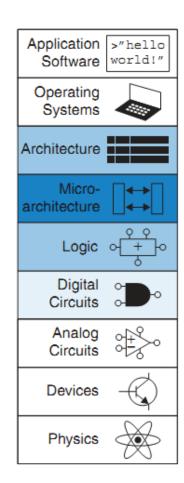

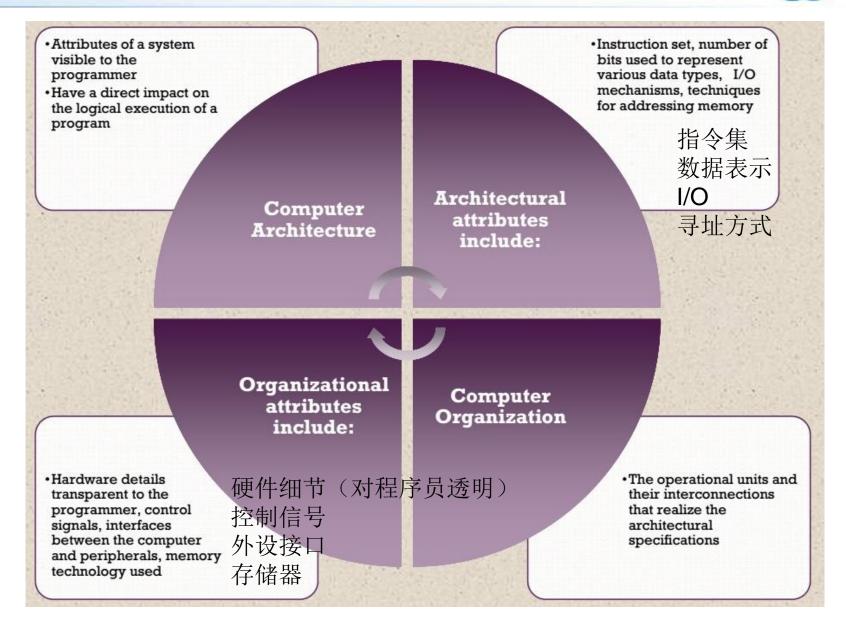

#### 计算机组成 vs. 计算机体系结构

- 计算机体系结构(Computer architecture)

- "程序员可见的机器属性", ISA

- G. M. Amdahl, 1964

- 程序员: 特指机器语言程序员

- 属性: 包含结构特征和功能特征

- 对物理机器的抽象

- 计算机组成(org & impl,也称µ-architecture)

- 计算机体系结构的逻辑实现,包括

- 实际机器的数据流和控制流的组成和逻辑设计等。

- 物理机器内部各事件的排序方式与控制方式

- 各部件的功能,以及各部件的联系。

# Computer Architecture & Organization

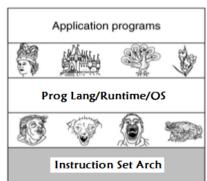

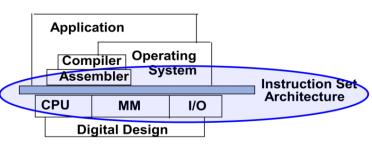

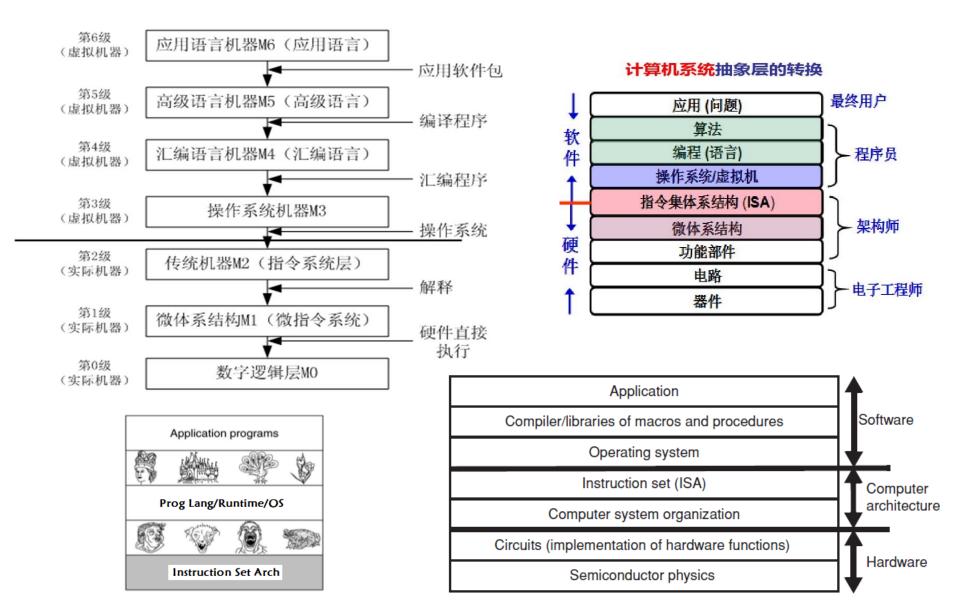

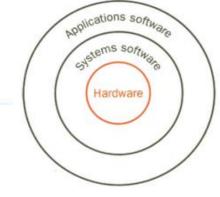

# 计算机系统的抽象层次: C语言计算机

#### 体系结构分类

- 按指令集特征

- 复杂指令集 (CISC)

- 精简指令集(RISC)

- 超标量 (Superscalar)

- 超流水线 (Superpipeline)

- 超长指令字(VLIW)

汤孟岩《并行多核体系结构基础》图1-6

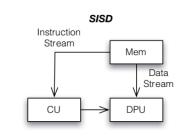

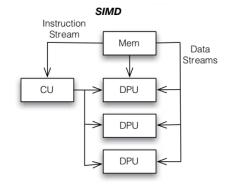

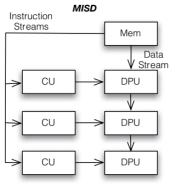

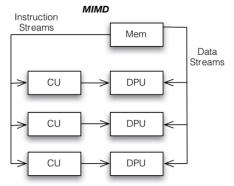

- 按并行执行特征: Flynn分类法 b

- 单指令流单数据流(SISD): Von Neumann Machine

- 单指令流多数据流(SIMD): 向量机, GPU

- 多指令流单数据流(MISD): 容错

- 多指令流多数据流(MIMD): 多核,多处理器

\$6.3图6-2

|             |          | Data Streams            |                               |  |  |

|-------------|----------|-------------------------|-------------------------------|--|--|

|             |          | Single                  | Multiple                      |  |  |

| Instruction | Single   | SISD: Intel Pentium 4   | SIMD: SSE instructions of x86 |  |  |

| Streams     | Multiple | MISD: No examples today | MIMD: Intel Core i7           |  |  |

### 体系结构的"7个伟大思想",

\$ (12)

- 使用"抽象"简化设计

- 如: 软硬件接口ISA

- 加速经常性事件

- the common case

- 通过并行提高性能

- 执行时长、吞吐率

- 通过流水线提高性能

- 吞吐率

- 通过预测提高性能

- 执行时长

- 存储系统层次化

- 执行时长

- 通过冗余提高性能

- 可靠性

# 计算思维(Computational Thinking)概念

- 周以真 (Jeannette M. Wing) @CS.CMU, 2006

- "计算思维是运用计算机科学的基础概念去求解问题、设计系统和理解人类行为的涵盖了计算机科学之广度的一系列思维活动"

- "计算思维与数学思维和艺术思维不同"

- 计算: 机器组织? MoC? 程序的语义? 编程模型?

- Tom Stuart, 《Understanding Computation》

- 语言影响思维: Jon Bentley, 算法十大师之一

- "我使用的Algol语言塑造了我的计算思维"

- 《编程珠玑(续)》

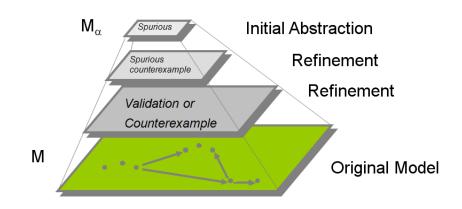

#### COD思维("系统思维"?)

- COD思维三要素——IIxx

- 模块化: Component Based Design

- The block diagram way of thinking

- 复杂性: "separation of concerns"

- 层次化: Abstraction/Refinement

- ABC范式:结构,行为,约束

- COD语言: 语法、语义、语用?

- -框图、原理图,时序图,CFG,DFG

- LTS、Automata、FSM,时态逻辑

- "计算机在干什么"?

#### 学习思路

- Yale Patt@ece.utexas

- Top-down: 适于"设计"——精化

- 从高级语言开始入手

- 前提是对底层有很好的理解

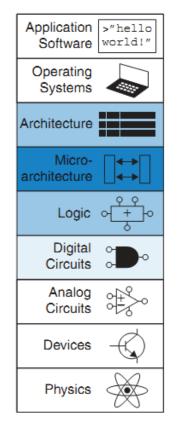

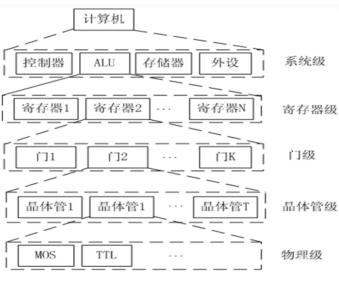

- Bottom-up: 适于"学习"

- 《计算机系统概论》

- 从最底层的**MOS**晶体管开关器件开始,逻辑门、锁存器、逻辑结构;

- 之后,有限状态机控制、顺序电路的实现、冯·诺伊曼结构、简单的计算机LC-3;

- 最后,LC-3的机器和汇编语言、C高级语言、递归等,最后是基本数据结构。

- 唐 (William Stallings): 自外而内

- 总线、存储、I/O、ALU、ISA、CPU

- COD: 自内而外

- ALU、ISA、CPU、存储、I/O

计算机设计者看到的计算机硬件系统

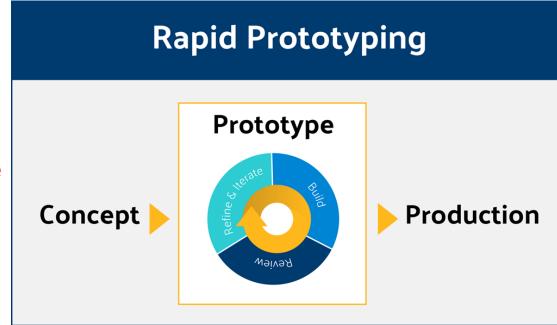

### 本课方法: 最小计算机快速原型法

- 快速原型法

- Build

- Review

- Refine & Iterate

- 工程化方法

- 原型=最小的计算机?

- ISA, CPU, SRAM, INTR;

- DRAM, Cache, Disk, VM;

- Bus, I/O;

- ALU

#### "害怕/不喜欢硬件"②

- David A. Patterson@CS.UCB

- "软件系统性能取决于软件设计者对系统硬件的理解程度。操作系统设计者、更多的软件工程师需要有较强的计算机组织与设计的背景知识"

- 程序执行结果不仅取决于算法和程序设计,而且取决于其**运行时环境** 和计算机体系结构!

- University of California at Berkeley in 1977

- Design and implementation of RISC I, first VLSI RISC Computer, foundation of the SPARC architecture, used by Sun

- leader of Redundant Arrays of Inexpensive Disks project (or RAID)

- Chair of the CS division at Berkeley

#### COD: HW or SW? 见Pvii

Read for culture

Review or read

| Chapter or Appendix                            | Sections                                        | Software focus | Hardware focus |

|------------------------------------------------|-------------------------------------------------|----------------|----------------|

| 1. Computer Abstractions                       | 1.1 to 1.11                                     |                | D N            |

| and Technology                                 | # 1.12 (History)                                | 000            | Ø              |

|                                                | 2.1 to 2.14                                     | 8              | Ø              |

| 2. Instructions: Language                      | 2.15 (Compilers & Java)                         | 8              |                |

| of the Computer                                | 2.16 to 2.20                                    | 8              | ğ              |

|                                                | (History)                                       | 8              | ğ              |

| E. RISC Instruction-Set Architectures          | (III) E.1 to E.17                               | 0              |                |

|                                                | 3.1 to 3.5                                      | Ø              | 8              |

| :                                              | 3.6 to 3.8 (Subword Parallelism)                | 8              | 8              |

| <ol> <li>Arithmetic for Computers</li> </ol>   | 3.9 to 3.10 (Fallacies)                         | 8              | 8              |

|                                                | (e) 3.11 (History)                              | 8              | B              |

| B. The Basics of Logic Design                  | B.1 to B.13                                     |                | Ø              |

|                                                | 4.1 (Overview)                                  | 8              | B              |

|                                                | 4.2 (Logic Conventions)                         |                | 8              |

|                                                | 4.3 to 4.4 (Simple Implementation)              | D              | Ď              |

|                                                | 4.5 (Pipelining Overview)                       | 8              | Š              |

| 4. The Processor                               | 4.6 (Pipelined Datapath)                        | Ø              | 8              |

|                                                | 4.7 to 4.9 (Hazards, Exceptions)                |                | 8              |

|                                                | 4.10 to 4.12 (Parallel, Real Stuff)             | 5              | D              |

|                                                | ( 4.13 (Verilog Pipeline Control)               |                | 8              |

|                                                | 4.14 to 4.15 (Fallacies)                        | 5              | Ď              |

|                                                | # 4.16 (History)                                | þ              | Ď              |

| D. Mapping Control to Hardware                 | D.1 to D.6                                      |                | 0              |

|                                                | 5.1 to 5.10                                     | Ď              | Ď,             |

| 5. Large and Fast: Exploiting                  | 5.11 (Redundant Arrays of<br>Inexpensive Disks) | 0              | 0              |

| Memory Hierarchy                               | ( 5.12 (Verilog Cache Controller)               |                | 0              |

|                                                | 5.13 to 5.16                                    | Š              | 8              |

|                                                | 5.17 (History)                                  | Ď              | 8              |

|                                                | 6.1 to 6.8                                      | Ď              | Ď              |

| 6. Parallel Process from Client                | e.9 (Networks)                                  | Ď              | Ø              |

| to Cloud                                       | 6.10 to 6.14                                    | 8              | 8              |

|                                                | 6.15 (History)                                  | Ď              | Ď              |

| A. Assemblers, Linkers, and the SPIM Simulator | A.1 to A.11                                     | 8              | Ø              |

| C. Graphics Processor Units                    | (iii) C.1 to C.13                               | Ø              | 8              |

| Read carefully X                               | Read if have time AC Reference                  |                | Ď              |

#### 刻苦刻苦刻苦: MIT

- 我在这里的第一学期上了一门叫《计算机系统设计》得本科课程,其辛苦程度真实一言难尽。

- 十五个星期内交了十次作业,作了六次课程设计。有的设计还分几个部分,分开交设计报告。所以设计报告大概也交了有十次左右。

- 最恐怖的是有一次,十天内要交六份作业或设计报告,而且当时正值其他几门课正在期中考试。抱怨是没有用的,老师说:"我很抱歉。但这门课很重要,请大家不停的工作"。

- 学生从一般的逻辑时序电路开始设计(数电都已忘得差不多了),核心是自行设计"麻雀虽小五脏俱全"得ALU,单指令周期CPU(single cycle CPU),多指令CPU(Multi-cycle CPU),以直到最后实现流水线(pipe line)32位MIPS CPU和Cache。

- 一门课下来,所有与计算机CPU有关的知识全部融会贯通。 硬件设计水平也有了很大提高(就是太累)。

#### 相关课程

- 美国UC Berkeley大学 "Machine Structure"2012年课程网站: http://inst.eecs.berkeley.edu/~cs61c/sp12/

- 美国UC Berkeley大学 "Components and Design Techniques for Digital System"2012年课程网站: http://inst.eecs.berkeley.edu/~cs150/sp12/

- 美国UC Berkeley大学 "Computer Architecture and Engineering"2012课程网站: http://inst.eecs.berkeley.edu/~cs152/sp12/

- 美国Stanford大学 "Computer Organization and Systems" 2012年课程网站: https://courseware.stanford.edu/pg/courses/281000/cs107-spring-2012

- 美国Stanford大学 "Digital Systems II"课程网站: http://www.stanford.edu/class/ee108b/

- 美国Stanford大学 "Digital Systems II"课程网站: http://www.stanford.edu/class/cs110/

- 美国Carnegie Mellon 大学 "Introduction to Computer Architecture"课程网站: http://www.cs.cmu.edu/~213/

- 美国Carnegie Mellon 大学 "Introduction to Computer Architecture"课程网站: <u>http://www.ece.cmu.edu/~ece447/</u>

- 美国Univ. Illinois at Urbana-Champaign "Computer Architecture II"课程网站: http://www.cs.uiuc.edu/class/sp11/cs232/

- 美国麻省理工学院(MIT)"Computation Structures"课程网站: http://6004.csail.mit.edu

#### 小结

- 核心概念

- 接口、系统思维、快速原型

- 计算机组成 vs. 计算机体系结构

- 计算机系统的层次化结构

- 挑战

- 数电

- 概念(名词)不一致

- 缺严谨定义: 自然语言而非形式化, 或示例说明

- 习惯差异: EE/CS, SW/HW, 中译

- 内容范围广: 全系统, 多层次

#### 调研报告一

- 选1, 下周5交

- 综述计算机技术的发展历程及热点问题

- 对比最新龙芯/Intel/ARM处理器的性能指标?

- 计算机的开机过程?

- C语言背后的计算机组成?

- getchar()函数的实现过程?

- PC系统活动与性能分析

- 跑一个Benchmark,给出结果?

- 每次执行同一个程序,结果都一样?

- 主频与计算性能的关系?

- 参考小论文格式

Thomas of