教材: 《VHDL 硬件描述语言与数字逻辑电路设计》候伯亨 顾新 西安电子科技大学 参考书: 《EDA 与数字系统设计》李国丽等 机械工业出版社

## 二、数字式竞赛抢答器

## 1、设计要求

设计一个可容纳四组参赛的数字式抢答器,每组设一个按钮供抢答者使用。抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用;设置一个主持人"复位"按钮,主持人复位后,开始抡答,第一信号鉴别锁存电路得到信号后,用指示灯显示抡答组别,扬声器发出2—3s的音响。

设置犯规电路,对提前抢答和超时答题(例如 3min)的组别鸣笛示警,并由组别显示电路显示出犯规组别。

设置一个计分电路,每组开始预置 10 分,由主持人记分,答对一次加 1 分,答错一次减 1 分。

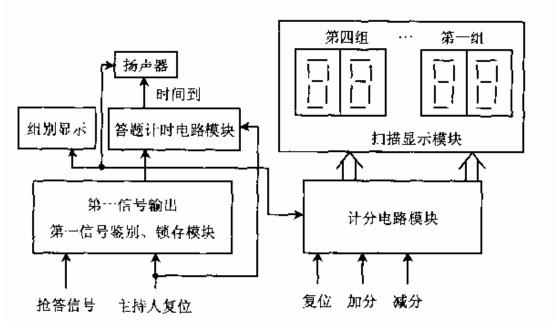

其系统框图如图 2 1 所示。

2 1 抢答器系统框图

## 2、设计提示

此设计问题可分为第一信号鉴别、锁存模块、答题计时电路模块、计分电路模块和扫描显示模块四部分。

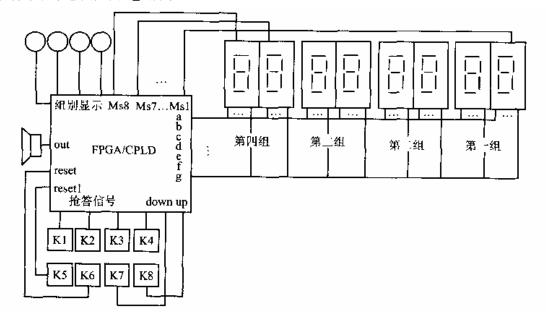

第一信号鉴别锁存模块的关键是准确判断出第一枪答者并将其锁存,在得到第一信号后,将输入端封锁,使其他组的抢答信号无效,可以用触发器或锁存器实现。设置抢答按钮 K1、K2、K3、K4,主持人复位信号 reset,扬声器驱动信号 out。

Reset=0 时,第一信号鉴别、锁存电路、答题计时电路复位,在此状态下,若有枪答按钮按下,鸣笛示警并显示犯规组别; reset=1 时,开始枪答,由第一信号鉴别锁存电路形成第一枪答信号,进行组别显示,控制扬声器发出音响,并启动答题计时电路,若计时时间到,主持人复位信号还没有按下则由扬声器发出犯规示警声。

计分电路是一个相对独立的模块,采用十进制加/减计数器、数码管数码扫描显示,设置复位信号 reset1、加分信号 up、减分信号 down, reset1=0 时,所有得分回到起始分(10分),且加分、减分信号无效; reset1=1 时,由第一信号鉴别、锁存电路的输出信号选择进行

加减分的组别,每按一次 up,第一抢答组加一分;每按一次 down,第一抢答组减一分。 硬件系统示意图如图 2\_2 所示。

图 2 2 数字抢答器硬件系统示意图