教材: 《VHDL 硬件描述语言与数字逻辑电路设计》候伯亨 顾新 西安电子科技大学 参考书: 《EDA 与数字系统设计》李国丽等 机械工业出版社

## 八、乘法器

## 1、设计要求

设计一个能进行两个十进制数相乘的乘法器,乘数和被乘数均小于 100,通过按键输入,并用数码管显示,显示器显示数字时从低位向高位前移,最低位为当前输入位。当按下相乘键后,乘法器进行两个数的相乘运算,数码管将乘积显示出来。

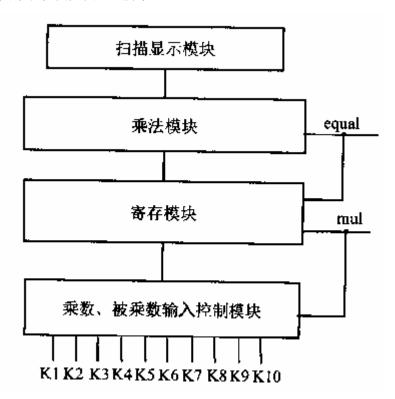

其系统框图如图 8-1 所示。

图 8-1 乘法器系统框图

## 2、设计提示

此设计问题可分为乘数和被乘数输入控制模块、寄存模块、乘法模块和扫描显示模块几部分。

乘数和被乘数的输入仍用数据开关 K1-K10 分别代表数字 1, 2, …, 9, 0, 用编码器 对数据开关 K1-K10 的电平信号进行编码,编码器真值表如表 5-1 所示。用两个数码管显示乘数,两个数码管显示被乘数。

设置"相乘"信号 mul, 当乘数输入完毕后, mul 有效, 使输入的乘数送寄存器模块寄存。再输入被乘数,显示在另两个数码管上。

设置"等于"信号叫 equal, 当乘数和被乘数输入后, equal 有效, 使被乘数送寄存模块寄存,同时启动乘法模块。

两数相乘的方法很多,可以用移位相加的方法,也可以将乘法器看成计数器,乘积的 初始值为零,每一个时钟周期将被乘数的值加到积上,同时乘数减一,这样反复执行,直到 乘数为零。

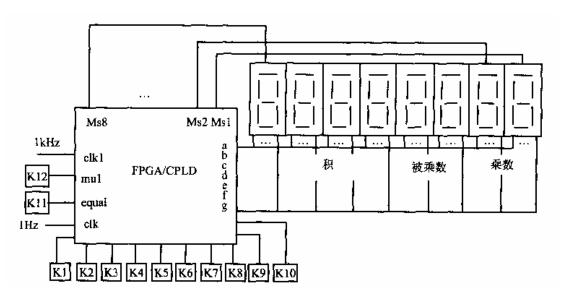

其硬件系统示意图如图 8-2 所示。

图 8-2 乘法器硬件系统示意图