Xilinx FPGA时钟资源

Xilinx的时钟资源分成了三种:PLL,DCM和MMCM,都在Xilinx的CMT (Clock ManagemenT)中可以找到。下面先介绍击中时钟的实现方式再来对Xilinx的时钟资源进行详细的分析。

PLL

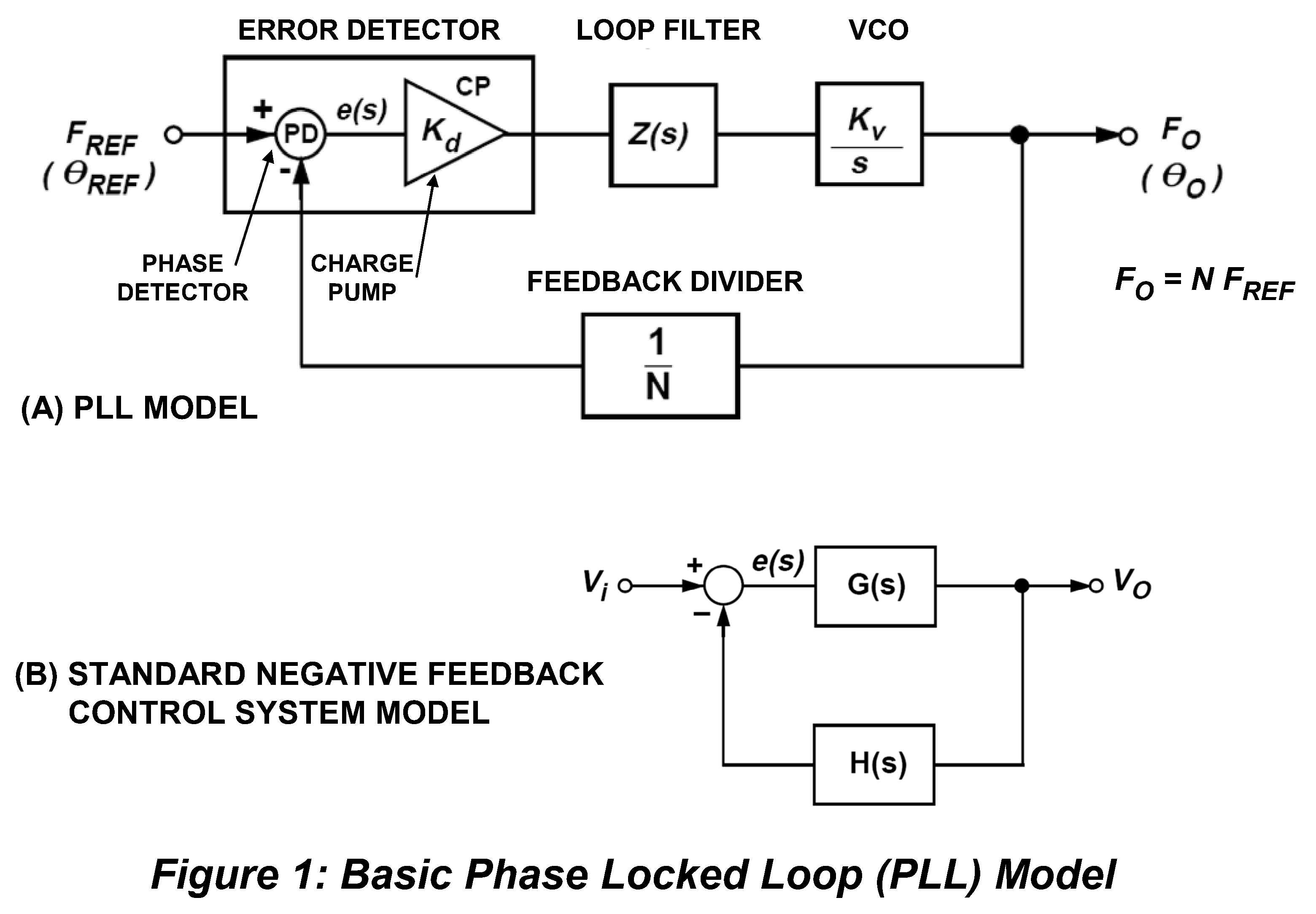

PLL的重点在于锁频,产生对应频率的时钟信号并不困难,但是任何时候时钟都会有抖动,因此需要一个电路结构对时钟的抖动进行跟踪和复原,也就是说需要一个负反馈的结构对时钟进行稳定,PLL就是其中一种结构,其原理如图\ref{figpll}所示,输入的频率通过鉴频鉴相器给出相位是超前还是落后了,然后给出相应的调整(输入信号超前了那么就增加VCO的频率,落后了就降低VCO的频率),输出的调整实际上是个电压值,这个电压值会控制VCO(压控振荡器)的输出频率,使得压控振荡器的输出频率能够跟得上输入信号频率的变化,压控振荡器的输出一路分频之后就可以作为信号输出,另一路经过N分频之后送回鉴频鉴相器和输入信号进行反馈,当然这里有个信号关系就是$f{VCO}=F_{in}\times N$;这里值得注意的问题是鉴频鉴相器的输出有可能会有抖动,同时系统的反馈并不是瞬间完成的,可能会造成频率震荡的问题(比如说一开始相位落后了,增大VCO的输出频率,相位又超前了,然后又降低VCO的频率,结果相位又落后了),因此在设计的时候鉴频鉴相器的输出需要滤波,以减少自身震荡和干扰的问题。不过现在很多高级的PLL都已经把这些电路集成在芯片内部了,不需要自己再考虑模拟部分的事情了。更多关于PLL的知识可以看AD公司的这份文档MT-086。

实验室已经成功使用的两款PLL芯片是LMK04616和Si5345

DLL

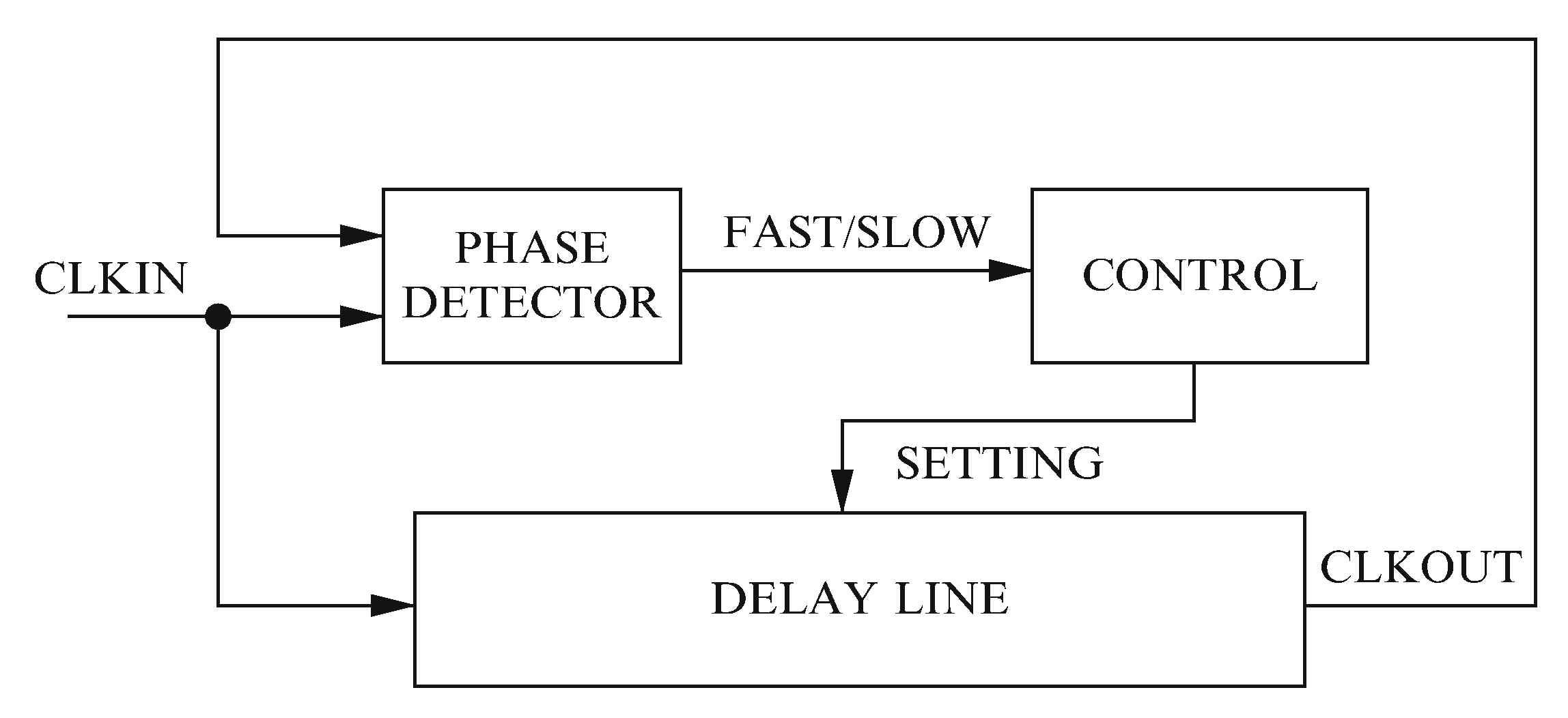

DLL的全称是digital Delay Locked Loop,原理和PLL很类似,只不过把结构中的VCO换成了延迟单元,如下图所示。一般DLL中的Phase detector只有两个输出,相位超前还是相位落后,也就是0或者1,延迟单元根据鉴相器的结果来调整输出频率实现对时钟相位和频率的调节。

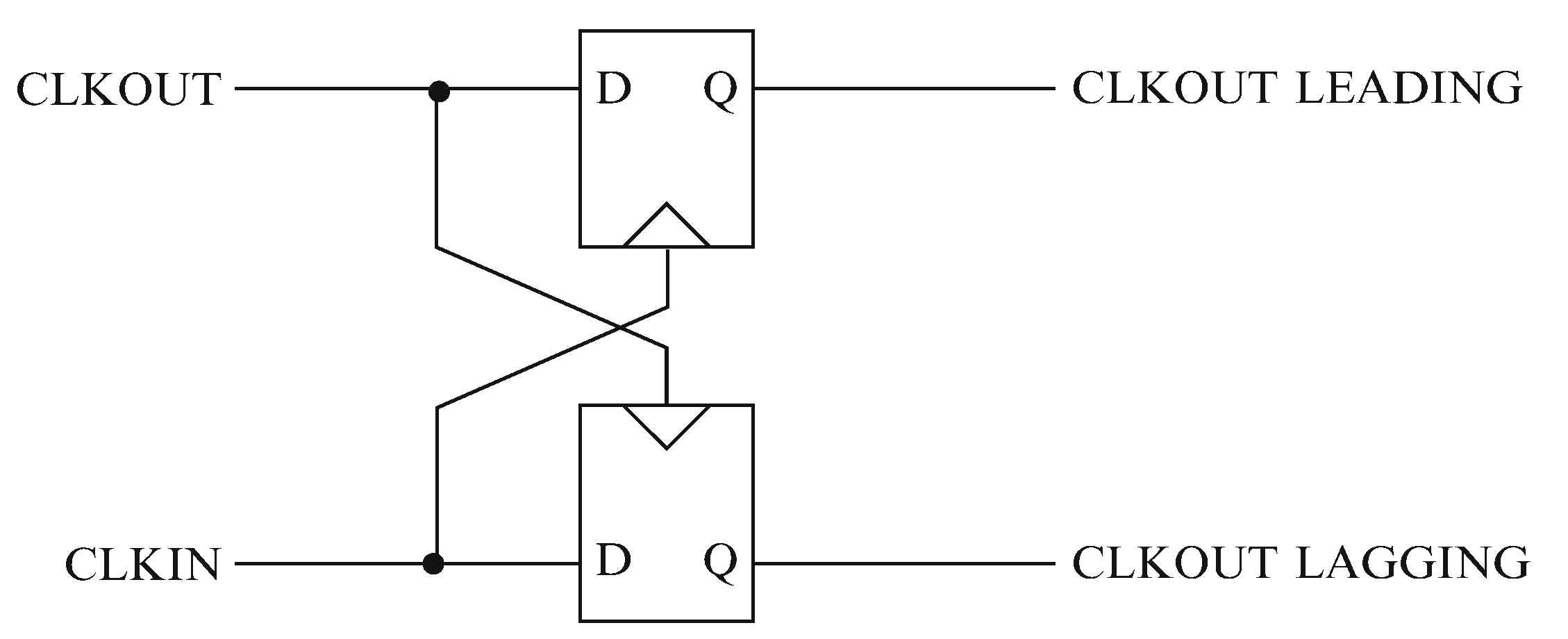

下图图是一种鉴相器的原理,简单分析下就能知道当两个时钟之间存在相位差的时候必然有个D触发器的输出是1,也就指示了两个时钟的超前和落后关系。这里需要考虑的就是两个D触发器的建立保持时间的问题,如果两个时钟靠得很近,就可能出现建立保持时间不满足的情况,这就涉及到DLL设计的工艺问题,D触发器的建立保持时间越小,这个DLL的相位稳定性就越好。更多的关于DLL的内容可以看这本书Clocking in Modern VLSI Systems。

DCM

DCM是Xilinx比较老的器件(Spartan-3、Virtex-4)中的时钟资源,可以提供时钟的倍频和分频、占空比调整、相位移动、去抖动等功能,当然现在低端7系列芯片已经很便宜了,DCM基本上已经用不太上了,这里只是简单的作一个介绍。

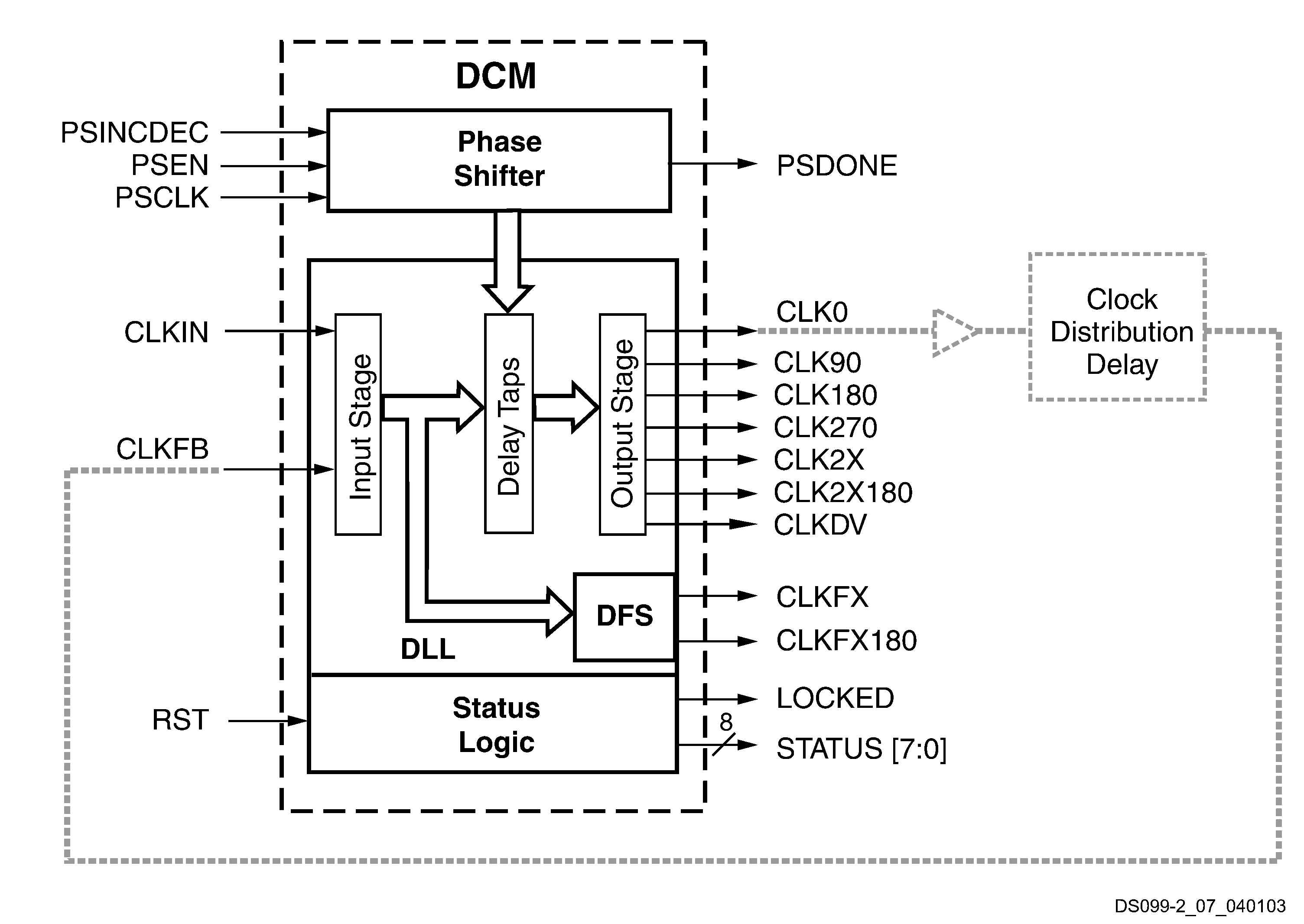

DCM的实现包含了4部分:输入级、输出级、DLL和相位调节器。如图~\ref{fig_xilinx_dcm}所示,Xilinx相当于把DLL所需要的所有电路都做进了FPGA里面,在使用的时候只要直接调用原语就可以了。

MMCM

MMCM是从Virtex-6系列开始引入FPGA的,全称是Mixed Mode Clock Manager,顾名思义也就是即有模拟的部分也有数字的部分,也就是在MMCM中集成了DLL和PLL两者的功能,可以实现精细的时钟频率和相位调整,甚至还可以分数分频,但是只能是0.125的倍数,不然会报一个Warning。

说道这里就不得不把Xilinx FPGA的时钟资源做个对比:

- 最古老的时钟资源就是DCM,所包含的功能有:去抖动、相位动态调节、倍频和分频和产生谐波频率的时钟,当然是在早期的Spartan-3和Virtex-4系列的FPGA的资源

- 接下来出现的时钟资源是PLL,在Virtex-5和Spartan-6中除了DCM之外还增加了PLL资源,除了DCM的功能之外,PLL还可以提供更小jitter的时钟,可以同时输出多个不同频率的时钟,同时支持的频率范围更广

- 接下来就是MMCM,在Virtex-6和7系列FPGA里面同时有MMCM和PLL两种资源,如前面所说MMCM相当于PLL+DLL,提供的功能更多,当然相应的占用芯片的面积也更大,我们平时用的最多的也是这个