配置

FPGA配置是实验室一个非常成熟的技术了,任何人都不应该在配置上翻车,下面是在用7系列FPGA时候整理的笔记。

配置文件格式

配置文件的格式可以分为以下五类

- BIT: 也就是我们常说的bit流,是一个二进制文件,实际上包含了两部分,一部分是头文件是给iMPACT看的,另一部分是配置到FPGA里面去的,用JTAG的时候直接下载这个文件就可以了

- RBIT:ASC II格式的BIT文件

- BIN:二进制文件,不包含头文件,全部都是直接配进FPGA的数据,可以用来作为其他外设对FPGA的配置

- MCS:ASC II格式文件,包含了地址、数据和校验,是用来写进flash的

- HEX:ASC II格式的配置文件,只有配置文件

配置管脚

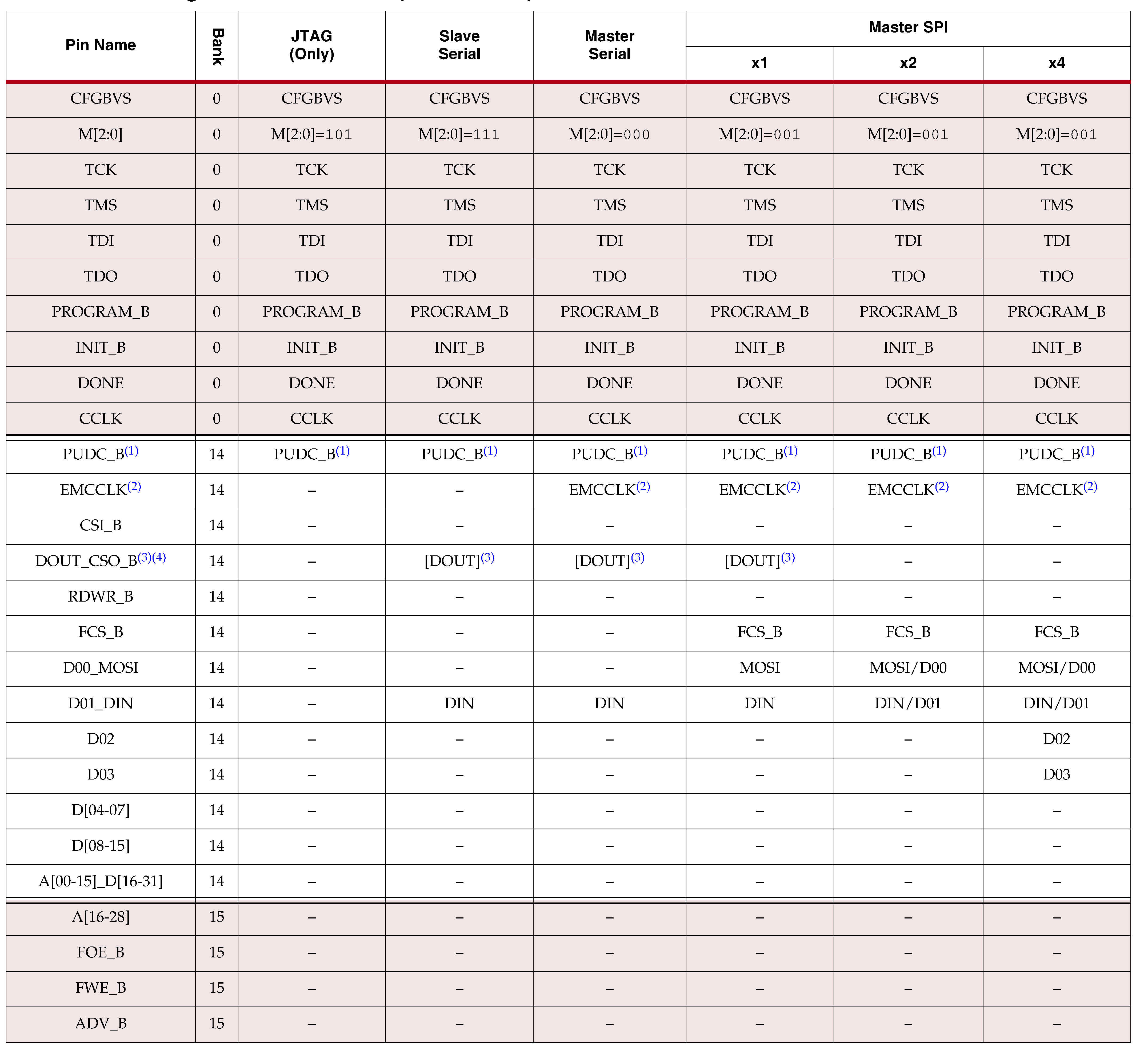

配置管脚分为两类,一类是所有模式专用的管脚,分布在专用的配置bank,电平标准和VCCO_0一致;另一种是复用的管脚分布在bank14和bank15,复用的管脚在FPGA配置完成之后可以用作普通IO来使用,后面会提到Remote configuration就是使用的这些管脚。平时最常用的两种配置的模式就是JTAG和Master SPIx4,配置管脚的说明见图\ref{fig_7config_pin}所示。

下面是对Master SPIx4模式管脚的说明

- CFGBVS(Configuration Banks Voltage Select)选择专用配置bank的电压,以及在配置过程中bank14和bank15的电压值

- M[2:0]选择配置模式,见上上图

- TCK JTAG配置模式使用的时钟

- TMS JTAG模式选择信号

- TDI JTAG模式数据输入

- TDO JTAG模式数据输出

- PROGRAM_B 低电平时复位FPGA配置,当外部把PROGRAM_B置为低电平时,FPGA的配置全部被清除,PROGRAM_B信号的上升沿FPGA从外部读入配置bit流。通过一个≤4.7kΩ的电阻将PROGRAM_B上拉倒VCCO_0,然后再通过一个按钮将其连接到GND,在按钮按下并松开之后,FPGA会进行重新配置

- INIT_B FPGA初始化或者出错信号。FPGA将内部逻辑清除并在配置中时,INIT_B为低电平,当配置完之后,INIT_B变为高阻态;如果外部将INIT_B拉低,FPGA将会延迟配置,一般用于FPGA上电延迟配置。用一个≤4.7kΩ的电阻将INIT_B上拉到VCCO_0

- DONE DONE管脚的高电平表示FPGA配置完成,DONE管脚是一个OD门。在FPGA内部,DONE管脚有一个10kΩ的上拉电阻,建议在片外使用一个 330Ω 的电阻来上拉DONE管脚

- CCLK Configuration Clock,在Master模式下,CCLK信号是一个输出信号,注意CCLK需要考虑信号完整性

- PUDC_B(Pull-Up During Configuration) 在FPGA上电到完成配置期间,PUDC_B低电平使能SelectIO的上拉电阻。PUDC_B需要通过一个≤1kΩ的电阻连上拉或者下拉到VCCO_0或者GND

- EMCCLK External Master Configuration Clock 在Master Mode下,如果需要快速配置,则使用EMCCLK作为配置时钟

- FCS_B Flash Chip Select FCS_B低电平使能SPI或者BPI flash的的片选信号。将这个信号连接到SPI或者BPI flash的片选信号管脚,同时使用一个≤4.7kΩ的电阻上拉到VCCO_14

JTAG和Master SPI}

JTAG模式是必须要有的最开始FPGA的逻辑必须通过这种方式送到FPGA里面去,值得注意的是JTAG模式是优先的,也就是说不管配置模式管脚配置成什么样,JTAG配置都是可以用的,也就是说在设计的时候直接把Mode管脚配置成Master SPIx4即可。

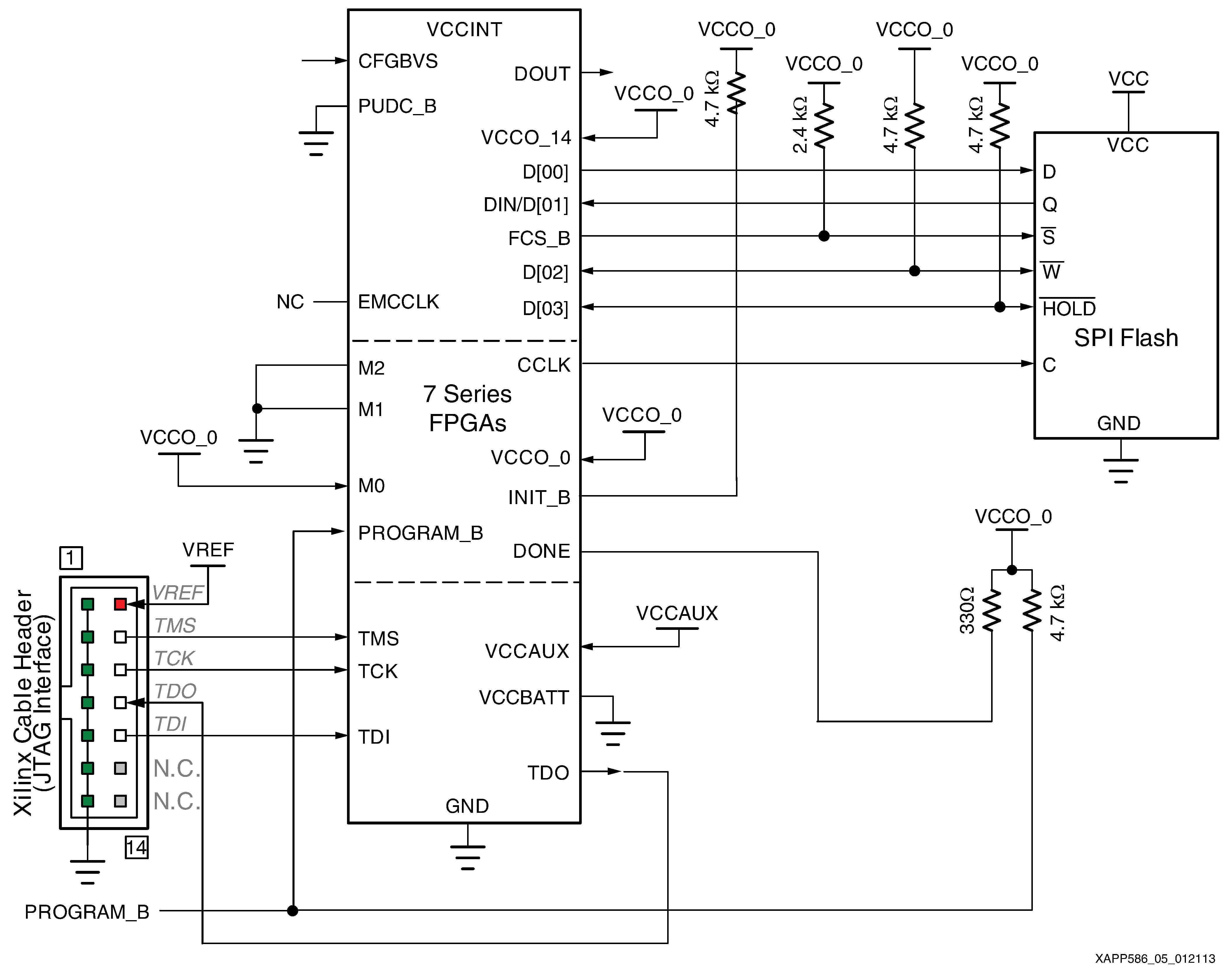

下图是Master SPIx4配置模式的连接图,注意这里的Master是指的FPGA作为Master对Flash进行操作,下面是一些详细的说明

- Done信号是OD门,需要一个上拉电阻

- INIT_B是一个双向OD门,也是需要一个上拉电阻

- CCLK需要考虑时序完整性

- 需要考虑SPI数据总线之间的串联电阻来减小过冲,电阻的阻值由仿真确定

- FPGA配置bank的VCCO必须和flash的VCC一样

- VCCBATT 是用来给存储AES key的SRAM加密的

上电顺序问题

FPGA在上电完成初始化之后,向 SPI flash 发出读信号,然后读出配置信号。

- FPGA 上电初始化

- 将 FCS_B 置低,选中 SPI flash

- 开始读配置文件

要求在 FPGA 读配置之前 SPI flash 先启动,一般来说flash上电时间是微秒量级的,而FPGA config bank上电初始化完成需要毫秒量级,也就是即使同时给FPGA和flash加电FPGA也是可以自动加载逻辑。

在实验室遇到过两种FPGA不能自动从flash中读取逻辑的情况:第一种是单独的DIF板可以自动从flash中读出配置,然后插上FEB板之后不能够自动加载逻辑了,这种情况主要的原因是VCC IO上电受到了FEB板的影响,FEB板和DIF板连接的管脚可能会有上拉管脚,这些管脚在flash上电完成前就给FPGA的管脚一个上拉电压,造成配置bank开始上电了,这个时候就会造成自动加载逻辑失败; 第二种情况是在同一板上配置bank的电压是3.3V,但是有些IO的电压是1.8V,1.8V上电在3.3V之前,这种情况下,FPGA的3.3V的IO会受到1.8V IO的影响,有一个电平值,使得FPGA以为可以开始读取配置了,但是这个时候flash还没有上电完成,使得自动加载逻辑失败。